随着电子设备向小型化、低功耗、高效率方向发展,开关稳压器因其高效的能量转换能力,已成为现代电源管理系统的核心。基于单电源的集成电路(IC)开关稳压器设计,更是将控制电路、功率开关管、反馈网络等高度集成于单一芯片,极大地简化了外围电路,提升了系统可靠性与功率密度。本文将深入探讨其设计原理、关键模块实现以及设计考量。

一、设计原理与拓扑结构

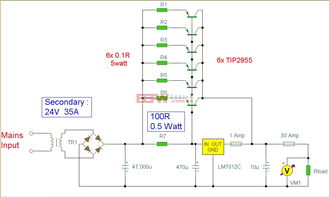

单电源IC开关稳压器通常采用降压(Buck)、升压(Boost)或升降压(Buck-Boost)等基本拓扑。其核心原理是通过控制内部功率金属氧化物半导体场效应晶体管(MOSFET)的开关状态,利用电感、电容等无源元件进行能量存储与释放,从而将不稳定的输入电压转换为稳定、可控的输出电压。脉冲宽度调制(PWM)是最常见的控制方式,通过调节开关占空比来精确调节输出电压。

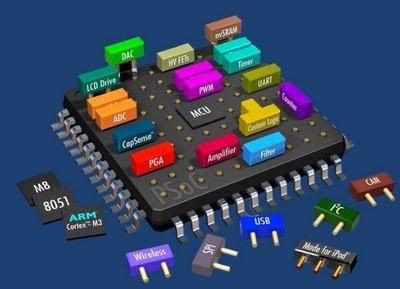

二、关键模块的集成电路实现

- 误差放大器与反馈网络:集成高增益误差放大器,将输出电压经电阻分压网络反馈的采样信号,与内部精密基准电压(如带隙基准源产生)进行比较,产生误差信号。这是实现高精度稳压的基础。

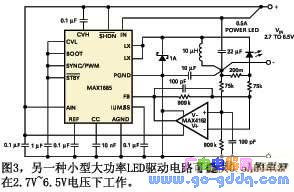

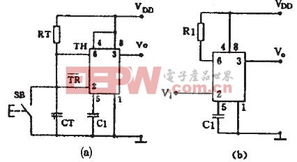

- PWM调制器与驱动器:误差信号送入PWM比较器,与锯齿波或三角波振荡器产生的斜坡信号比较,生成占空比可控的PWM脉冲。该脉冲经由栅极驱动器进行功率放大,以足够快的速度和高电流驱动能力控制功率MOSFET的导通与关断,减小开关损耗。

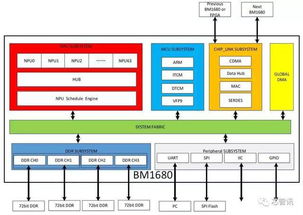

- 功率开关管:采用先进的CMOS或BCD工艺,将导通电阻(Rds(on))极低的高压功率MOSFET集成在芯片上。这是实现高效率和高功率密度的关键,其设计需在导通损耗、开关损耗、芯片面积与耐压能力之间取得平衡。

- 保护电路:完善的IC集成了过温保护(OTP)、过流保护(OCP)、欠压锁定(UVLO)以及短路保护等模块。这些电路实时监测工作状态,确保系统在异常条件下安全关断,提升了可靠性。

- 振荡器与偏置电路:内部振荡器产生恒定的开关频率(从数百kHz到数MHz),决定了外部电感、电容的尺寸。偏置电路为芯片内部所有模块提供稳定的工作电压和电流。

三、核心设计考量与挑战

- 效率优化:效率是开关稳压器的生命线。设计重点在于降低功率通路的各类损耗,包括:功率MOSFET的导通损耗与开关损耗、栅极驱动损耗、电感直流电阻(DCR)损耗以及控制电路静态功耗。采用同步整流技术(用MOSFET替代续流二极管)可显著提升中低负载效率。

- 稳定性与瞬态响应:由电感、电容和负载构成的外部环路需与内部补偿网络匹配,确保在所有工作条件下系统稳定,相位裕量充足。需优化控制环路带宽,以实现对负载阶跃变化的快速响应,减小输出电压过冲与下冲。

- 电磁干扰(EMI)抑制:高速开关动作是EMI的主要来源。在IC设计层面,可采用频率抖动(Spread Spectrum)技术分散开关能量,优化驱动器斜率控制(Slew Rate Control)以减缓开关边沿。需在版图布局上精心安排功率地与信号地,减少寄生参数引起的噪声耦合。

- 动态范围与灵活性:优秀的单电源开关稳压器IC需适应宽范围的输入电压(如3V至40V)和输出电压(可调或固定),并提供可编程的开关频率、软启动等功能,以满足不同应用场景的需求。

四、应用与未来趋势

此类高度集成的开关稳压器IC广泛应用于消费电子、工业控制、汽车电子及物联网设备中。未来发展趋势聚焦于:

- 更高开关频率(>3MHz):以进一步缩小外围电感、电容体积,实现超薄设计。

- 更高集成度:将更多被动元件(如高频电感)甚至负载点(POL)稳压器进行封装级集成(如SiP)。

- 更智能的数字控制:集成数字脉冲宽度调制(DPWM)和微控制器内核,实现自适应环路补偿、多相位并联及复杂的系统级电源管理序列。

- 宽禁带半导体集成:探索将GaN或SiC功率器件与CMOS控制电路单片集成,追求极限效率与功率密度。

基于单电源的集成电路开关稳压器设计是一个涉及模拟电路、功率器件、控制理论及半导体工艺的综合性工程。通过精心的架构设计、电路优化和版图实现,现代电源管理IC在效率、尺寸和智能性上不断突破,持续为电子设备提供更高效、更紧凑、更可靠的“能量心脏”。