555定时器集成电路自1971年问世以来,凭借其稳定性高、成本低廉、功能灵活等特点,在电子设计领域占据了举足轻重的地位。它既能作为精确的定时器,也能作为方波发生器、脉冲调制器、电压比较器等,应用极其广泛。本文主要探讨555集成电路在定时器应用中的核心设计原理、经典电路配置及其设计要点。

一、555集成电路的核心结构与工作原理

555集成电路内部由两个比较器、一个RS触发器、一个放电晶体管以及一个分压网络(三个5kΩ精密电阻串联,故名“555”)构成。其核心工作原理基于电容的充放电过程。通过外接电阻和电容(RC网络)设定时间常数,内部比较器监测电容电压,并与由分压网络设定的参考电压(通常为1/3 Vcc和2/3 Vcc)进行比较,从而控制RS触发器的状态,最终在输出端产生高电平或低电平。放电晶体管则在特定阶段为电容提供放电通路。

二、经典定时器应用电路模式

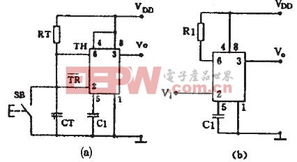

在定时应用中,555主要有两种基本工作模式:单稳态模式和非稳态(多谐振荡)模式。

- 单稳态模式:在此模式下,电路构成一个“一次触发”的定时器。当触发引脚(第2脚)接收到一个低电平脉冲(低于1/3 Vcc)时,输出端(第3脚)会跳变为高电平并维持一段时间。该时间长度(即定时周期T)完全由外接的电阻R和电容C决定,计算公式为:T ≈ 1.1 R C。在此期间,电路对新的触发信号不响应(除非被复位),直到定时结束,输出恢复低电平,等待下一次触发。此模式常用于延时开关、脉冲宽度调制、触摸开关等。

- 非稳态模式:在此模式下,电路无需外部触发即可自行振荡,产生连续的矩形波(方波)输出。它内置了充放电循环。输出高电平时间(Thigh)和低电平时间(Tlow)由两个电阻(R1, R2)和电容C共同决定。具体公式为:

- T_high ≈ 0.693 (R1 + R2) C

- T_low ≈ 0.693 R2 C

- 总周期 T = Thigh + Tlow,输出频率 f = 1 / T。

通过调节R1、R2和C的值,可以方便地获得所需的频率和占空比。此模式常用于时钟信号生成、LED闪烁器、音调发生器等。

三、定时器应用设计要点与考量

设计一个基于555的可靠定时器电路,需综合考虑以下因素:

- 定时精度与稳定性:定时周期主要依赖于RC时间常数。应选择温度系数小、精度高的电阻(如金属膜电阻)和电容(如聚酯薄膜电容或钽电容),以减小环境温度变化带来的误差。电源电压Vcc的稳定性也直接影响内部比较器的阈值电压,进而影响定时精度,因此建议使用稳压电源。

- 元件参数选择:

- 电阻R:通常建议在1kΩ到几MΩ之间选择。阻值过小会导致电源电流过大;阻值过大(如>10MΩ)则可能因漏电流等因素导致定时不准。

- 电容C:定时电容的范围可以从几皮法(pF)到几百微法(μF)。对于长定时(数分钟至数小时),需要使用大容量电解电容,但需注意其较大的漏电流和容差会显著影响精度,此时可考虑使用较小电容配合CMOS版本的555(如7555)以获得更长定时。

- 触发与复位设计:在单稳态电路中,触发信号必须是一个短暂的低电平脉冲(宽度应小于定时时间),且需确保其电压能可靠地降至1/3 Vcc以下。复位引脚(第4脚)通常接高电平,若需外部强制中断定时,可将其接低电平。设计时应注意为触发和复位信号添加适当的去抖动电路(如RC滤波或施密特触发器),防止误动作。

- 输出驱动能力:标准555的输出端可提供高达200mA的拉电流或灌电流,足以直接驱动LED、小型继电器或扬声器。当驱动感性负载(如继电器线圈)时,必须在负载两端反向并联一个续流二极管,以吸收关断时产生的反向感应电动势,保护芯片。

- 电源去耦:为抑制噪声和防止振荡,应在555的电源引脚(第8脚)和地(第1脚)之间尽可能靠近芯片的位置,连接一个0.01μF到0.1μF的陶瓷去耦电容。

四、进阶应用与改进

基础电路之上,可以通过添加外部元件实现更复杂的功能。例如:

- 在单稳态模式的控制电压端(第5脚)施加一个调制电压,可以线性改变定时周期,实现电压控制定时。

- 将两个555级联,可以构成长延时定时器或复杂的时序发生器。

- 对于需要更高精度和更低功耗的应用,可以选择CMOS工艺的555(如ICL7555、TLC555等),其工作电流更小,输入阻抗更高,更适合与高阻值电阻配合实现超长定时。

结论

555集成电路作为定时器,其设计核心在于理解其内部工作机制并合理配置外部RC网络。单稳态和非稳态两种模式为从简单延时到连续脉冲发生的各类定时需求提供了简洁高效的解决方案。通过精心的元件选型、稳定的电源供应和必要的抗干扰措施,设计者能够构建出满足广泛需求、经济可靠的定时电路。尽管当今微控制器在定时功能上更为灵活,但555芯片以其无需编程、即连即用的特性,在许多对成本和开发周期敏感的应用中,依然保持着不可替代的价值。