自1965年戈登·摩尔提出集成电路上可容纳的晶体管数量约每两年增加一倍的著名预言以来,“摩尔定律”已成为半导体行业近六十年的发展蓝图与核心驱动力。随着晶体管尺寸逼近物理极限,工艺复杂度与制造成本呈指数级攀升,业界和学术界都在严肃探讨一个根本性问题:摩尔定律是否已然终结?

一、摩尔定律的现状:放缓与演进

严格意义上,经典的、以晶体管尺寸等比例缩微为核心的摩尔定律确实已进入“放缓期”或“后摩尔时代”。传统硅基CMOS工艺在5纳米及以下节点面临量子隧穿效应、寄生效应、功耗墙、散热等严峻物理挑战,单纯依靠尺寸微缩带来的性能提升和成本下降效益正在急剧递减。因此,摩尔定律在“密度翻倍”的原始表述上正趋于物理极限。

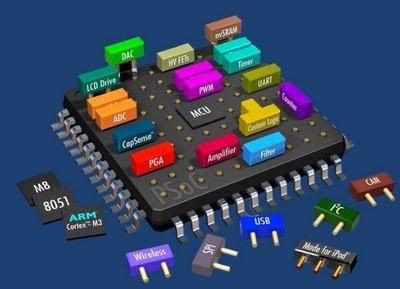

这并不意味着集成电路创新的终结。业界更倾向于认为摩尔定律正在“演进”。它从单一的几何尺度缩放,扩展为以系统性能、功耗效率、功能集成和总体成本为核心的多维度量。例如,通过先进封装技术(如2.5D/3D集成、Chiplet芯粒)将不同工艺、不同功能的芯片进行异质集成,在系统层面延续了“等效摩尔定律”的发展路径。

二、后摩尔时代集成电路发展的核心方向

面对后摩尔时代的挑战,大规模集成电路的发展不再依赖单一技术突破,而是走向多路径协同创新的“超越摩尔”(More than Moore)范式。主要发展方向包括:

- 架构创新与异构计算:当工艺红利减弱,计算效率的提升重任转向了芯片架构。特定领域架构(DSA),如GPU、NPU、TPU等AI加速器的兴起,以及CPU、GPU、FPGA、ASIC等组成的异构计算系统,通过软硬件协同设计,针对特定负载(如AI、图形、信号处理)实现数量级的能效提升。

- 先进封装与系统级集成:通过硅中介层、扇出型封装、3D堆叠等技术,将多个裸片(Chiplet)集成在一个封装内。这允许将大芯片分解为小型化、模块化的芯粒,分别采用最适合的工艺(如计算芯粒用先进工艺,模拟/射频芯粒用成熟工艺)制造,再“组装”起来,大幅降低设计复杂度和成本,并提升良率与系统性能。

- 新材料与新器件探索:在延续硅基主线的研究新型半导体材料(如二维材料、氧化物半导体)和新型器件原理(如隧道场效应晶体管、自旋电子器件、存算一体器件)。其中,存算一体技术旨在打破“冯·诺依曼瓶颈”,直接在存储器中完成计算,特别适合数据密集型的AI应用,有望实现极致的能效比。

- 光电集成与硅光子学:将光传输引入芯片内部或芯片之间,利用光信号高速、低耗、抗干扰的特性,解决电互连在带宽和功耗上面临的瓶颈,为数据中心、高性能计算等场景提供关键支撑。

三、后摩尔时代对集成电路设计的深刻影响

技术路线的变革,从根本上重塑了集成电路设计的方法论与范式:

- 设计重心转移:从传统的、以标准单元库和EDA工具流为核心的“逻辑物理设计”,转向涵盖系统架构定义、芯粒划分、互连协议、封装协同、热管理、系统验证的 “系统级-芯片-封装协同设计” 。设计团队必须具备更全面的系统视野。

- IP复用与Chiplet生态:基于标准互连协议(如UCIe)的Chiplet模式,使得高性能IP(如高速SerDes、HBM控制器、计算核)可以作为预制件进行商业化复用,极大地加速复杂芯片的开发,但同时也对接口标准化、测试、可靠性提出了全新挑战。

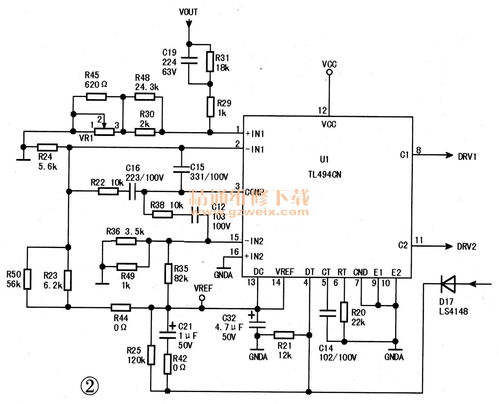

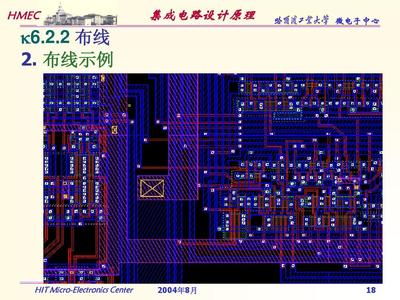

- EDA工具升级:EDA工具需要支持从系统架构探索、多物理场(电、热、应力)协同仿真,到3D堆叠布局布线、异构集成验证等全流程能力,智能化(AI for EDA)和平台化将成为关键。

- 软硬件深度融合:芯片设计越来越需要与上层算法、编译器、操作系统乃至应用场景深度耦合。硬件设计为软件优化留出接口,软件则充分挖掘硬件潜力,形成一体化设计闭环。

结论

摩尔定律的“经典时代”或许已近尾声,但它所代表的创新精神与指数级进步追求并未熄灭。我们正步入一个更为多元、开放和协作的“后摩尔时代”。大规模集成电路的将不再由工艺节点的数字单一驱动,而是由架构创新、异质集成、新材料器件与系统级设计共同谱写。集成电路设计工程师的角色,也将从晶体管层面的“微观雕刻家”,演变为驾驭芯片、封装乃至整个计算系统的“宏观架构师”。这场深刻的范式转移,虽充满挑战,但也为全球半导体产业打开了新一轮波澜壮阔的创新大门。